|

Looking back at the code - the vector concatenation thing on the left hand side in the. A combinational circuit is one in which the present output is a function of only the present inputs - there is no memory. Full Adder: We will continue to learn more examples with Combinational Circuit - this time a full adder. Verilog Full Adder Example.The barrier is crumbling because of the similarity between hardware description languages and programming languages. Up until now, the barriers were so high for software engineers who wanted to learn hardware design that few explored the space. Here's an introduction to hardware design in Verilog for the uninitiated.6.375 Spring 2006 L03 Verilog 2 - Design Examples 14 Behavioral GCD model is written within a single always block with C like structure module gcdGCDUnitbehav( parameter W 16 ) ( input W-1:0 inA, inB, output W-1:0 Y ) reg W-1:0 A, B, Y, swap integer done always () begin done 0 A inA B inB while ( done ) begin if ( A < B )In the near future, embedded systems designers will be able to use hardware and software interchangeably depending on which best solves a specific design problem.

Verilog Example Code How To Implement PulseYou can do everything in this article with the FPGA development kits that are available today from major FPGA manufacturers.Several things have changed that make it easier for software engineers to participate in hardware design. We'll look at how to implement pulse width modulation (PWM) in software and then turn the design into a logic block that can run from an FPGA and be controlled via software using a memory-mapped I/O interface. Behavcounter.v.This article offers an example of this new design process using an FPGA. For more information of Verilog, go to: How to Use Verilog HDL Examples. The always construct, highlighted in red text, describes how the counter should behave. This example describes an 8 bit loadable counter with count enable.The syntax and structure of Verilog is similar to that of the C programming language, as the examples in this article will illustrate.At the same time, hardware is getting easier to update and change. On the hardware side, Verilog is often the popular choice (though both VHDL and Verilog are popular). As you know, C is the lingua franca of embedded software design.

Verilog Example Code Full Adder ExampleVerilog Example Code Download The NewIn other words, it affords you the flexibility during design and debugging to choose the best way to handle these taskseither in software or hardware.Tools are available from FPGA vendors that enable a designer with a little knowledge of hardware to develop an embedded system for programmable logic, such as an FPGA. Programmable logic changes the method for designing embedded systems by enabling you to change the hardware as easily as the software. Just as a software developer can make a quick edit, recompile, and then download the new code into memory, hardware designers using programmable logic have a similar capability. That's no longer entirely true. Figure 1 shows a PWM waveform of about 33% duty cycle.PWM is used in many applications, most frequently to control analog circuitry. The duty cycle, or on time, is defined as the ratio of the pulse width to the period. Usually the period and pulse width are specified. With programmable logic and some hardware knowledge, software engineers can take advantage of the benefits of hardware to improve their systems.A PWM controller produces a stream of pulses like those shown in Figure 1. 103).Generally speaking, PWM is implemented in hardware because the output signal must be continuously updatedgoing high from the start of each period for the proper time, then low for the remainder of the period. If the duty cycle is increased, the motor will turn faster likewise, if the duty cycle is decreased the motor will slow.For more information about PWM, consult Michael Barr's Beginner's Corner article “ Introduction to Pulse Width Modulation” (September 2001, p. For example, if a stream of PWM pulses is sent to a motor, it will turn at a rate proportional to the duty cycle (from 0% to 100%). Watch mission impossible 123moviesThe infinite loop then sets the output pin high, waits for time_on time units to elapse, sets the output low, waits for time_off , and then repeats the cycle for the next period.Listing 2 shows a simple Verilog module implementing an 8-bit wide register with an asynchronous reset. Listing 1 shows the C code for PWM.Listing 1: A bit-banging PWM controller implemented entirely in software voidpwmTask(uint32_t pulse_width, uint32_t period)Based on the pulse_width and period arguments to this function, the PWM calculates the amount of time the output will be high and low. Writing such a PWM controller in software is a relatively trivial task and helps illustrate what we will do in Verilog shortly. Download windows 10 ovaOnce the device is powered on, every element of the hardware is always executing. Both Verilog and C are case sensitive as well.Of course, one key difference between hardware and software is how they “run.” A hardware design consists of many elements all running in parallel. In fact, the begin and end keywords are optional for single-statement blocks, just like C's curly braces. Verilog's if.then.else is similar to that of C, except that the keywords begin and end are used instead of curly braces. An = operator is also used to test equality. A semicolon is used to end each statement and the comment delimiters are the same (both /* */ and // are recognized). Software is executed serially, so that each line of code is executed only after the line before it is complete (except for nonlinearities on interrupts or at the behest of an operating system).A Verilog module starts with the module keyword followed by the name of the module and the port list, which is a list of the names of all the inputs and outputs of the module. Variables may exist with a valid value, but most of the time they're not involved in any processing.This difference in behavior translates to differences in the way we program hardware and software code. The rest of the software can be considered dormant, unlike the rest of the hardware. If there's just one processor, only one instruction is actually being executed at a time. However, they're always “running.”In contrast, only one small portion of an entire software design (even one with multiple software tasks defined) is being executed at any one time. Therefore, the line declaring a as a wire is not necessary. All parts have a signal by the same name implicitly declared as a wire. These types differ in function. Note that all of the input and outputs appear in both the port list in the first line of the module and in the port declarations section.In Verilog, two types of internal signals are widely used: reg and wire.

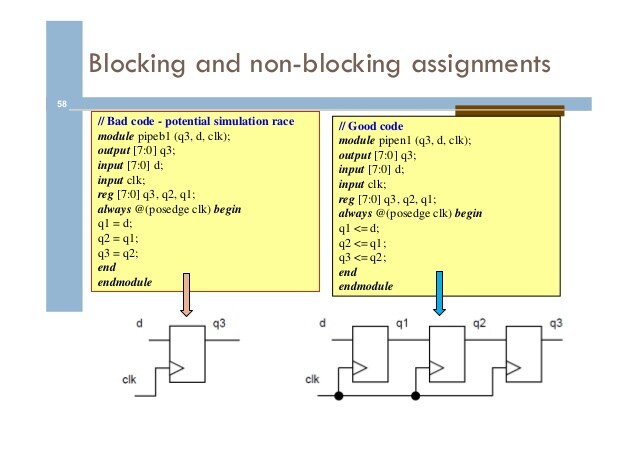

This module infers a reg ister because of the way the always block (a type of procedural block) is written. The code in Listing 2 has one internal signal of type reg that's 8 bits wide and called out. Both signal types can appear on the right-hand side of the assignment operator inside or outside of any procedural block.It's important to understand that using the reg keyword doesn't necessarily mean the compiler will create a register. These are often used in sensitivity lists. The Verilog keywords for rising edge and falling edge are posedge and negedge , respectively. The group of expressions inside the parentheses of the always statement is called the sensitivity list it's of the form:The code inside the always block is executed whenever any expression in its sensitivity list is true.

0 Comments

Leave a Reply. |

AuthorRita ArchivesCategories |

RSS Feed

RSS Feed